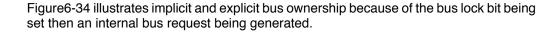

## SECTION 6 BUS OPERATION

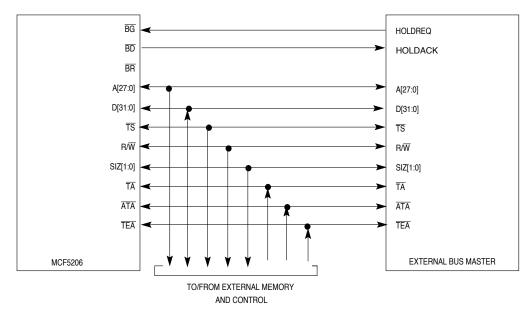

The MCF5206 bus interface supports synchronous data transfers that can be terminated synchronously or asynchronously and burst or burst-inhibited between the MCF5206 and other devices in the system. This section describes the function of the bus, the signals that control the bus, and the bus cycles provided for data-transfer operations. Operation of the bus is defined for transfers initiated by the MCF5206 as a bus master and for transfers initiated by an alternate bus master (Note: "alternate bus master" and "external bus master" are used interchangeably). The section includes descriptions of the error conditions, bus arbitration, and the reset operation.

## 6.1 FEATURES

The following list summarizes the key bus operation features:

- · As many as 28 bits of address and 32 bits of data

- · Access 8-, 16-, and 32-bit port sizes

- · Generates byte, word, longword, and line size transfers

- Bus arbitration for alternate masters

- · Burst and burst-inhibited transfer support

- · Internal termination generation

- · Termination generation for alternate masters

## 6.2 BUS AND CONTROL SIGNALS

## 6.2.1 Address Bus (A[27:0])

These three-state bidirectional signals provide the location of a bus transfer (except for interrupt-acknowledge transfers) when the MCF5206 is the bus master. When an alternate bus master controls the bus, the address signals are examined when transfer start (TS) is asserted to determine if the MCF5206 should assert chip-select, DRAM control, and/or transfer terminal signals. During an interrupt-acknowledge access, address lines A[27:5] are driven high, A[1:0] are driven low, and the address lines A[4:2] indicate the interrupt level being acknowledged.

## NOTE

The ColdFire core outputs 32 bits of address to the internal bus controller. Of these 32 bits, only A[27:0] are output to pins on the MCF5206. The output of A[27:24] depends on the setting of PAR[3:0] in the Pin Assignment Register (PAR) in the SIM. Refer to **Section 7.3.2.10 Pin Assignment Register** (PAR) on how to program the Pin Assignment Register (PAR).

## 6.2.2 Data Bus (D[31:0])

These three-state bidirectional signals provide the general-purpose data path between the MCF5206 and all other devices. The data bus can transfer 8, 16, 32, or 128 bits of data per bus transfer. A write cycle drives all 32 bits of the data bus regardless of the port width and operand size.

## 6.2.3 Transfer Start (TS)

The MCF5206 asserts this three-state bidirectional signal for one clock period to indicate the start of each bus cycle. During alternate master accesses, the MCF5206 monitors transfer start ( $\overline{TS}$ ) to detect the start of each alternate master bus cycle to determine if chip-select, DRAM, and/or transfer termination signals should be asserted.

## 6.2.4 Read/Write (R/W)

This three-state bidirectional signal defines the data transfer direction for the current bus cycle. A high (logic one) level indicates a read cycle; a low (logic zero) level indicates a write cycle. When an alternate bus master is controlling the bus, the MCF5206 monitors this signal to determine if chip-select or DRAM control signals should be asserted.

## 6.2.5 Size (SIZ[1:0])

These three-state bidirectional signals indicate the data size for the bus cycle. When an alternate bus master is controlling the bus, the MCF5206 monitors these signals to determine the data size for asserting the appropriate memory control signals. Table 6-1 shows the definitions of the SIZx encoding.

|      |      | -                  |

|------|------|--------------------|

| SIZ1 | SIZ0 | TRANSFER SIZE      |

| 0    | 0    | Longword (4 Bytes) |

| 0    | 1    | Byte               |

| 1    | 0    | Word (2 Bytes)     |

| 1    | 1    | Line (16 Bytes)    |

#### Table 6-1. SIZx Encoding

## 6.2.6 Transfer Type (TT[1:0])

These three-state output signals indicate the type of access for the current bus cycle. Table 6-2 lists the definitions of the TTx encodings.

| TT1 | TT0 | TRANSFER TYPE                |

|-----|-----|------------------------------|

| 0   | 0   | Normal Access                |

| 0   | 1   | Reserved                     |

| 1   | 0   | Debug Access                 |

| 1   | 1   | CPU Space/Acknowledge Access |

Table 6-2. Transfer Type Encoding

The MCF5206 does not sample TT[1:0] during alternate master transfers.

## 6.2.7 Access Type and Mode (ATM)

This three-state output signal provides supplemental information for each transfer cycle type. Table 6-3 lists the encoding for normal, debug and CPU space/acknowledge transfer types.

| TRANSFER TYPE           | INTERNAL TRANSFER MODIFIER      | ATM (TS=0) | ATM (TS=1) |

|-------------------------|---------------------------------|------------|------------|

| 00                      | Supervisor Code                 | 1          | 1          |

| (Normal Access)         | Supervisor Data                 | 0          | 1          |

|                         | User Code                       | 1          | 0          |

|                         | User Data                       | 0          | 0          |

| 10                      | Supervisor Code                 | 1          | 1          |

| (Debug Access)          | Supervisor Data                 | 0          | 1          |

| 11                      | CPU Space - MOVEC Instruction   | 0          | 0          |

| (CPU Space/Acknowledge) | Interrupt Acknowledge - Level 7 | 1          | 0          |

|                         | Interrupt Acknowledge - Level 6 | 1          | 0          |

|                         | Interrupt Acknowledge - Level 5 | 1          | 0          |

|                         | Interrupt Acknowledge - Level 4 | 1          | 0          |

|                         | Interrupt Acknowledge - Level 3 | 1          | 0          |

| Γ                       | Interrupt Acknowledge - Level 2 | 1          | 0          |

|                         | Interrupt Acknowledge - Level 1 | 1          | 0          |

| T T                     |                                 |            |            |

Table 6-3. ATM Encoding

The MCF5206 does not sample ATM during alternate master transfers.

## 6.2.8 Asynchronous Transfer Acknowledge (ATA)

This active-low asynchronous input signal indicates the successful completion of a requested data transfer operation. Asynchronous transfer acknowledge ( $\overline{ATA}$ ) is an input signal from the referenced slave device indicating completion of the transfer. ( $\overline{ATA}$ ) is synchronized internal to the MCF5206.

## NOTE

The internal synchronized version of  $(\overline{ATA})$  will be referred to as "internal asynchronous transfer acknowledge." Because of the time required to internally synchronize  $\overline{ATA}$ , during a read cycle, data is latched on the rising edge of CLK when the

MOTOROLA

internal asynchronous transfer acknowledge is asserted. Consequently, data must remain valid for at least one CLK cycle after the assertion of ATA. Similarly, during a write cycle, data is driven until the rising edge of CLK when the internal asynchronous transfer acknowledge is asserted.

$\overline{\text{ATA}}$  must be driven for one full CLK to ensure that the MCF5206 properly synchronizes the signal. For the MCF5206 to accept the transfer as successful with an  $\overline{\text{ATA}}$ , transfer error acknowledge  $\overline{\text{TEA}}$  must be negated until the internal asynchronous transfer acknowledge is asserted or the transfer will be completed with a bus error.

Asynchronous transfer acknowledge (ATA) is not used for termination during DRAM accesses.

## 6.2.9 Transfer Acknowledge (TA)

This three-state bidirectional active-low synchronous signal indicates the successful completion of a requested data transfer operation. During MCF5206-initiated transfers, transfer acknowledge (TA) is an input signal from the referenced slave device indicating completion of the transfer. For the MCF5206 to accept the transfer as successful with a transfer acknowledge, TEA must be negated throughout the transfer.

TA is not used for termination during MCF5206-initiated DRAM accesses.

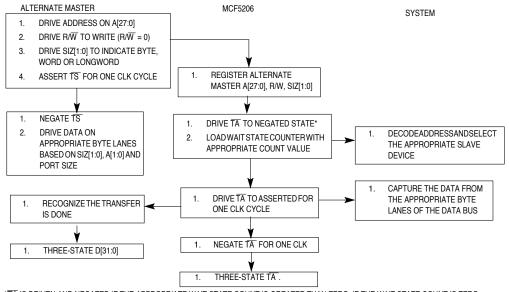

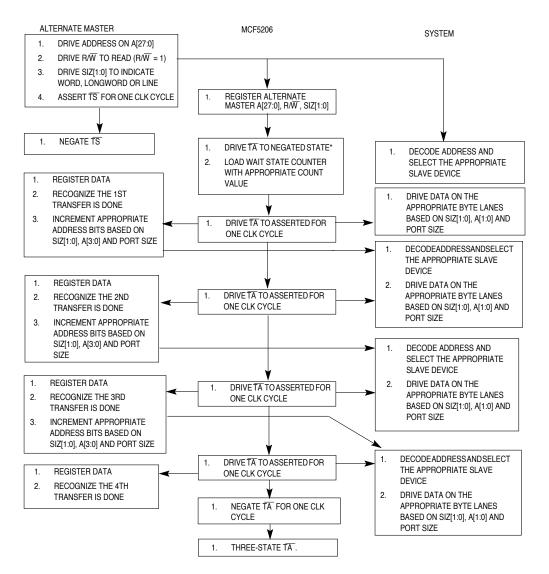

When an alternate master is controlling the bus, the MCF5206 can drive  $\overline{TA}$  to indicate the completion of the requested data transfer. If the alternate master-requested transfer is to a chip-select or default memory, the assertion of  $\overline{TA}$  is controlled by the number of wait states and the setting of the alternate master automatic acknowledge (EMAA) bit in the Chip-Select Control Registers (CSCRs) or the Default Memory Control Register (DMCR). If the alternate master-requested transfer is a DRAM access, the MCF5206 drives  $\overline{TA}$  as an output and is asserted at the completion of the transfer.

## 6.2.10 Transfer Error Acknowledge (TEA)

The external slave asserts this active-low input signal to indicate an error condition for the current transfer. The assertion of  $\overline{\text{TEA}}$  immediately aborts the bus cycle. The assertion of  $\overline{\text{TEA}}$  has precedence over the assertion of asynchronous transfer acknowledge ( $\overline{\text{ATA}}$ ) and transfer acknowledge ( $\overline{\text{TA}}$ ).

#### NOTE

TEA can be asserted up to one clock after the assertion of asynchronous transfer acknowledge ( $\overline{ATA}$ ) and still be recognized.

TEA has no effect during DRAM accesses.

MCF5206 USER'S MANUAL Rev 1.0

## 6.3 BUS EXCEPTIONS

## 6.3.1 Double Bus Fault

If the MCF5206 experiences a double bus fault, it will enter the halted state. To exit the halt state, reset the MCF5206.

## 6.4 BUS CHARACTERISTICS

The MCF5206 uses the address bus (A[27:0]) to specify the location for a data transfer and the data bus (D[31:0]) to transfer the data. Control and attribute signals indicate the beginning and type of a bus cycle as well as the address space, direction, and size of the transfer. The selected device or the number of wait states programmed in the memory control register (the Chip-Select Control Register (CSCR), the DRAM Controller Control Registers (DCCR, including the DRAM Controller Timing Register (DCTR)), or the Default Memory Control Register (DMCR)) control the length of the cycle.

The MCF5206 CLK is distributed internally to provide logic timing. All bus signals are synchronous with the rising edge of CLK with the exception of row address strobes ( $\overline{RAS}[1:0]$ ) and column address strobes ( $\overline{CAS}[3:0]$ ), which can be asserted and negated synchronous with the falling edge of CLK.

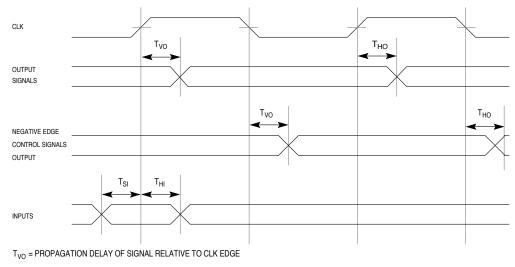

Inputs to the MCF5206 (other than the interrupt priority level signals ( $\overline{IPLx}$ ), reset in ( $\overline{RSTI}$ ) and  $\overline{ATA}$  signals) are synchronously sampled and must be stable during the sample window defined by  $t_{si}$  and  $t_{hi}$  (as shown in Figure 6-1) to guarantee proper operation. The asynchronous  $\overline{IPLx}$ ,  $\overline{RSTI}$  and  $\overline{ATA}$  signals are internally synchronized to resolve the input to a valid level before being used.

Outputs to the MCF5206 begin to transition on the rising CLK edges, with the exception of  $\overline{RAS}[1:0]$  and  $\overline{CAS}[3:0]$ , which begin to transition on the falling CLK edges. Specifically,  $\overline{RAS}[1:0]$  is asserted and negated synchronous with the falling edge of CLK, while  $\overline{CAS}[3:0]$  is asserted synchronous with the falling edge of CLK and can be negated synchronous with either the falling edge or the rising edge of CLK.

During alternate master accesses where the MCF5206 drives  $\overline{TA}$  as an output,  $\overline{TA}$  will always be driven negated for one CLK cycle before being placed in a high-impedence state.

T<sub>HO</sub> = OUTPUT HOLD TIME RELATIVE TO CLK EDGE

T<sub>SI</sub> = REQUIRED INPUT SETUP TIME RELATIVE TO CLK EDGE

T<sub>HI</sub> = REQUIRED INPUT HOLD TIME RELATIVE TO CLK EDGE

#### Figure 6-1. Signal Relationships to CLK

## 6.5 DATA TRANSFER MECHANISM

The MCF5206 supports byte, word, and longword operands and allows accesses to 8-, 16-, and 32-bit data ports. With the MCF5206, you can select the port size of the specific memory, enable internal generation of transfer termination, and set the number of wait states for the external slave being accessed by programming the Chip-Select Control Registers (CSCRs), the DRAM Controller Control Registers (DCCRs), and the Default Memory Control Register (DMCR). For more information on programming these registers, refer to the SIM, Chip-Select, and DRAM Controller sections.

## NOTE

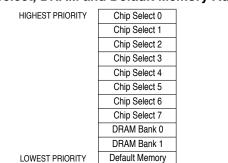

The MCF5206 compares the address for the current bus transfer with the address and mask bits in the Chip-Select Address Registers (CSAR), DRAM Controller Address Registers (DCARs), the Chip-Select Mask Registers (CSMR), and DRAM Controller Mask Registers (DCMR), looking for a match. The priority is listed in Table 6-4 (from highest priority to lowest priority):

MCF5206 USER'S MANUAL Rev 1.0

#### Table 6-4. Chip Select, DRAM and Default Memory Address Decoding Priority

The MCF5206 will compare the address and mask in chip-select 0 - 7 control registers (chip-select 0 is compared first), then the address and mask in DRAM bank 0 - 1 control registers. If the address does not match in either or these, the MCF5206 will use the control bits in the Default Memory Control Register (DMCR) to control the bus transfer. If the Default Memory Control Register (DMCR) control bits are used, no chip-select or DRAM control signals will be asserted during the transfer.

## 6.5.1 Bus Sizing

The MCF5206 reads the port size for each transfer from either the Chip-Select Control Registers (CSCRs), the DRAM Controller Control Registers (DCCRs), or the Default Memory Control Register (DMCR) at the start of each bus cycle. This allows the MCF5206 to transfer operands from 8-, 16-, or 32-bit ports. The size of the transfer is adjusted to accommodate the port size indicated. A 32-bit port must reside on data bus bits D[31:0], a 16-bit port must reside on data bus bits D[31:24]. This requirement ensures that the MCF5206 correctly transfers valid data to 8-, 16-, and 32-bit ports.

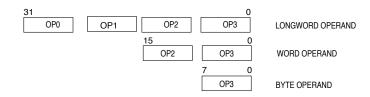

The bytes of operands are designated as shown in Figure 6-2. The most significant byte of a longword operand is OP0; OP3 is the least significant byte. The two bytes of a word length operand are OP2 (most significant) and OP3. The single byte of a byte length operand is OP3. These designations are used in the figures and descriptions that follow.

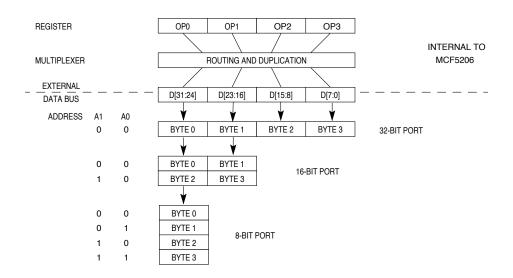

Figure 6-3 shows the required organization of data ports on the MCF5206 for 8-, 16-, and 32 bit devices. The four bytes shown are connected through the internal data bus and data multiplexer to the external data bus. This path is how the MCF5206 supports programmable port sizing and operand misalignment. The data multiplexer establishes the necessary connections for different combinations of address and data sizes.

Figure 6-3. MCF5206 Interface to Various Port Sizes

The multiplexer takes the four bytes of the 32-bit bus and routes them to their required positions. For example, OP3 can be routed to D[7:0], as would be the normal case when interfacing to a 32-bit port. OP3 can be routed to D[23:16] for interfacing to a 16-bit port, or it can be routed to D[31:24] for interfacing to an 8-bit port. The operand size, address, and port size of the memory being accessed determines the positioning of bytes.

The MCF5206 can burst anytime the port size of the external slave being accessed is smaller than the operand size. If bursting is enabled, the MCF5206 will burst transfers depending on the port size and operand alignment. For any transfer, the number of bytes transferred during a bus cycle is equal to or less than the size indicated by the SIZx outputs. For example, during the first bus cycle of a longword transfer to a 16-bit port where bursting is enabled, the SIZx outputs will remain constant throughout the transfer and will indicate that four bytes are to be transferred, although only two bytes are moved at a time.Table 6-5 lists the encodings for the SIZx bits for each port size for transfers where bursting is both enabled and disabled.

A[0] and A[1] also affect operation of the data multiplexer. During an operand transfer, A[31:2] indicate the longword base address of that portion of the operand to be accessed; A[1] and A[0] indicate the byte offset from the base. Table 6-6 lists the encoding of A[1] and A[0] and the corresponding byte offset from the longword base.

MCF5206 USER'S MANUAL Rev 1.0

|                 |      | 32-BIT        | PORT |                |      | 16 -BIT       | PORT |                | 8-BIT PORT |               |      |                |

|-----------------|------|---------------|------|----------------|------|---------------|------|----------------|------------|---------------|------|----------------|

| OPERAND<br>SIZE |      | sting<br>Bled |      | sting<br>Bited |      | sting<br>Bled |      | sting<br>Bited |            | sting<br>Bled |      | STING<br>BITED |

|                 | SIZ1 | SIZ0          | SIZ1 | SIZ0           | SIZ1 | SIZ0          | SIZ1 | SIZ0           | SIZ1       | SIZ0          | SIZ1 | SIZ0           |

| BYTE            | 0    | 1             | 0    | 1              | 0    | 1             | 0    | 1              | 0          | 1             | 0    | 1              |

| WORD            | 1    | 0             | 1    | 0              | 1    | 0             | 1    | 0              | 1          | 0             | 0    | 1              |

| LONGWORD        | 0    | 0             | 0    | 0              | 0    | 0             | 1    | 0              | 0          | 0             | 0    | 1              |

| LINE            | 1    | 1             | 0    | 0              | 1    | 1             | 1    | 0              | 1          | 1             | 0    | 1              |

| Table 6-5. S | SIZx Encod | ing for Burst | <ul> <li>and Bursting</li> </ul> | g-Inhibited Ports |

|--------------|------------|---------------|----------------------------------|-------------------|

|              |            |               |                                  |                   |

## Table 6-6. Address Offset Encoding

| A1 | A0 | OFFSET   |

|----|----|----------|

| 0  | 0  | +0 Byte  |

| 0  | 1  | +1 Byte  |

| 1  | 0  | +2 Bytes |

| 1  | 1  | +3 Bytes |

Table 6-7 lists the bytes that should be driven on the data bus during read cycles by the slave device being accessed. The entries shown as Byte X are portions of the requested operand that are read. The operand being read is defined by SIZ[1], SIZ[0], A[0], and A[1] for the bus cycle. Bytes labeled X are "don't cares" and are not required during that read cycle. Bytes labeled "-" indicates that this transfer is not valid.

| TRANSFER<br>SIZE | SI   | ZE   | ADD | RESS | EXTERN   | 32 BIT<br>IAL DATA |         | QUIRED | EXTERN   | PORT<br>AL DATA<br>EQUIRED | 8 BIT PORT<br>EXTERNAL DATA<br>BYTES REQUIRED |        |   |   |

|------------------|------|------|-----|------|----------|--------------------|---------|--------|----------|----------------------------|-----------------------------------------------|--------|---|---|

|                  | SIZ1 | SIZ0 | A1  | A0   | D[31:24] | D[23:16]           | D[15:8] | D[7:0] | D[31:24] | D[23:16]                   | D[31:24]                                      |        |   |   |

| BYTE             |      |      | 0   | 0    | Byte 0   | Х                  | Х       | Х      | Byte 0   | Х                          | Byte 0                                        |        |   |   |

|                  |      |      | 0   | 1    | Х        | Byte 1             | Х       | Х      | Х        | Byte 1                     | Byte 1                                        |        |   |   |

|                  | 0 1  | 0    | 1   | 1    | 0        | Х                  | Х       | Byte 2 | Х        | Byte 2                     | Х                                             | Byte 2 |   |   |

|                  |      |      | 1   | 1    | Х        | Х                  | Х       | Byte 3 | Х        | Byte 3                     | Byte 3                                        |        |   |   |

| WORD             |      | 1 0  |     | 0    | 0        | Byte 0             | Byte 1  | Х      | Х        | Byte 0                     | Byte 1                                        | Byte 0 |   |   |

|                  |      |      |     |      |          |                    | 0       | 1      | -        | -                          | -                                             | -      | - | - |

|                  | 1    |      | 1   | 0    | Х        | Х                  | Byte2   | Byte 3 | Byte 2   | Byte 3                     | Byte 2                                        |        |   |   |

|                  |      |      | 1   | 1    | -        | -                  | -       | -      | -        | -                          | Byte 3                                        |        |   |   |

| LONGWORD         |      |      | 0   | 0    | Byte 0   | Byte 1             | Byte 2  | Byte 3 | Byte 0   | Byte 1                     | Byte 0                                        |        |   |   |

|                  |      |      | 0   | 1    | -        | -                  | -       | -      | -        | -                          | Byte 1                                        |        |   |   |

|                  | 0    | 0    | 1   | 0    | -        | -                  | -       | -      | Byte 2   | Byte 3                     | Byte 2                                        |        |   |   |

|                  |      |      | 1   | 1    | -        | -                  | -       | -      | -        | -                          | Byte 3                                        |        |   |   |

MOTOROLA

.

| TRANSFER<br>SIZE | SI        | ZE | ADD | RESS | EXTERN   | 32 BIT PORT<br>AL DATA BYTES REQUIRED |         |        | 16 BIT PORT<br>EXTERNAL DATA<br>BYTES REQUIRED |          | 8 BIT PORT<br>EXTERNAL DATA<br>BYTES REQUIRED |        |

|------------------|-----------|----|-----|------|----------|---------------------------------------|---------|--------|------------------------------------------------|----------|-----------------------------------------------|--------|

|                  | SIZ1 SIZ0 |    |     |      | D[31:24] | D[23:16]                              | D[15:8] | D[7:0] | D[31:24]                                       | D[23:16] | D[31:24]                                      |        |

| LINE             |           |    | 0   | 0    | Byte 0   | Byte 1                                | Byte 2  | Byte 3 | Byte 0                                         | Byte 1   | Byte 0                                        |        |

|                  | 1 1       |    |     | 0    | 1        | -                                     | -       | -      | -                                              | -        | -                                             | Byte 1 |

|                  |           | 1  | 1   | 0    | -        | -                                     | -       | -      | Byte 2                                         | Byte 3   | Byte 2                                        |        |

|                  |           |    | 1   | 1    | -        | -                                     | -       | -      | -                                              | -        | Byte 3                                        |        |

| Table 6-7. Data Bus Requirement for Read Cycles (Continued) |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

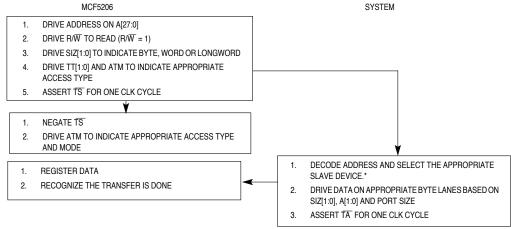

Figure 6-4 is a flowchart for read transfers to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer.

<sup>\*</sup>TO INSERT WAIT STATES, TA IS DRIVEN NEGATED.

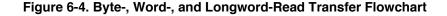

Figure 6-5 shows a longword supervisor code read from a 32-bit port.

Figure 6-5. Longword-Read Transfer From a 32-Bit Port (No Wait States)

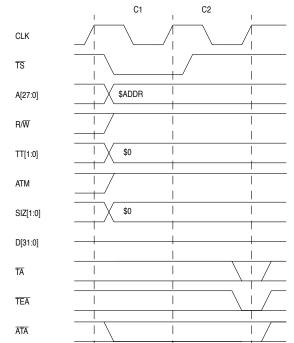

## Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type. Access type and mode (ATM) identifies the transfer as reading code. The read/write ( $R/\overline{W}$ ) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven low to indicate a longword transfer. The MCF5206 asserts transfer start ( $\overline{TS}$ ) to indicate the beginning of a bus cycle.

## Clock 2 (C2)

During C2, the MCF5206 negates transfer start ( $\overline{TS}$ ), drives access type and mode (ATM) high to identify the transfer as supervisor. The selected device(s) places the addressed data onto D[31:0] and asserts the transfer acknowledge ( $\overline{TA}$ ). At the end of C2, the MCF5206 samples the level of  $\overline{TA}$  and if  $\overline{TA}$  is asserted, latches the current value of D[31:0]. If  $\overline{TA}$  is asserted, the transfer of the longword is complete and the transfer terminates. If  $\overline{TA}$  is negated, the MCF5206 continues to sample  $\overline{TA}$  and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted. If the bus monitor timer is enabled and  $\overline{TA}$  is not

MOTOROLA

asserted before the programmed bus monitor time is reached, the cycle will be terminated with an internal bus error.

Table 6-8 lists the combinations of SIZ[1:0], A[1:0] and the corresponding pattern of the data transfer for write cycles from the internal multiplexer of the MCF5206 to the external data bus. For example, if a longword transfer is generated to a 16-bit port, the MCF5206 will start the cycle with A[1:0] set to \$0 and read the first word. The MCF5206 will then increment A[1:0] to \$2 and will read the second word. The data for both word reads will be sampled from DATA[31:16]. Bytes labeled X are "don't cares."

| TRANSFER | SI   | ZE   | ADD | RESS | EXTERN   | EXTERNAL DATA BUS CONNECTION |         |        |  |  |

|----------|------|------|-----|------|----------|------------------------------|---------|--------|--|--|

| SIZE     | SIZ1 | SIZ0 | A1  | A0   | D[31:24] | D[23:16]                     | D[15:8] | D[7:0] |  |  |

|          | 0    | 1    | 0   | 0    | OP3      | Х                            | Х       | Х      |  |  |

| DVTC     |      |      | 0   | 1    | OP3      | OP3                          | Х       | Х      |  |  |

| BYTE     |      |      | 1   | 0    | OP3      | Х                            | OP3     | Х      |  |  |

|          |      |      | 1   | 1    | OP3      | OP3                          | Х       | OP3    |  |  |

|          | 1    | 0    | 0   | 0    | OP2      | OP3                          | Х       | Х      |  |  |

| WORD     |      |      | 0   | 1    | OP3      | Х                            | Х       | Х      |  |  |

|          |      |      | 1   | 0    | OP2      | OP3                          | OP2     | OP3    |  |  |

|          |      |      | 1   | 1    | OP3      | Х                            | Х       | Х      |  |  |

|          | 0    | 0    | 0   | 0    | OP0      | OP1                          | OP2     | OP3    |  |  |

|          |      |      | 0   | 1    | OP1      | Х                            | Х       | Х      |  |  |

| LONGWORD |      |      | 1   | 0    | OP2      | OP3                          | Х       | Х      |  |  |

|          |      |      | 1   | 1    | OP3      | Х                            | Х       | Х      |  |  |

|          | 1    | 1    | 0   | 0    | OP0      | OP1                          | OP2     | OP3    |  |  |

|          |      |      | 0   | 1    | OP1      | Х                            | Х       | Х      |  |  |

| LINE     |      |      | 1   | 0    | OP2      | OP3                          | Х       | Х      |  |  |

|          |      |      | 1   | 1    | OP3      | Х                            | Х       | Х      |  |  |

Table 6-8. Internal to External Data Bus Multiplexer - Write Cycle

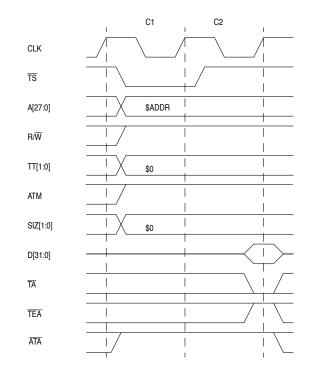

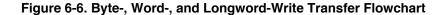

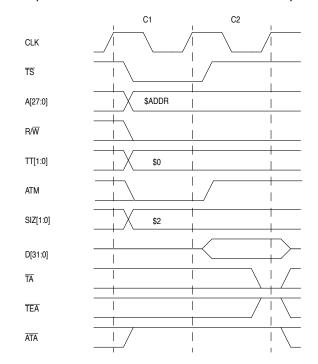

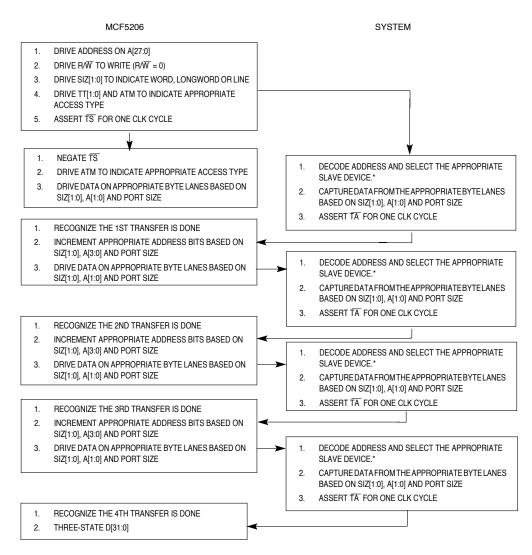

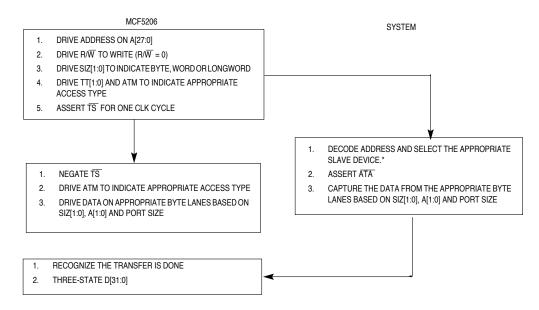

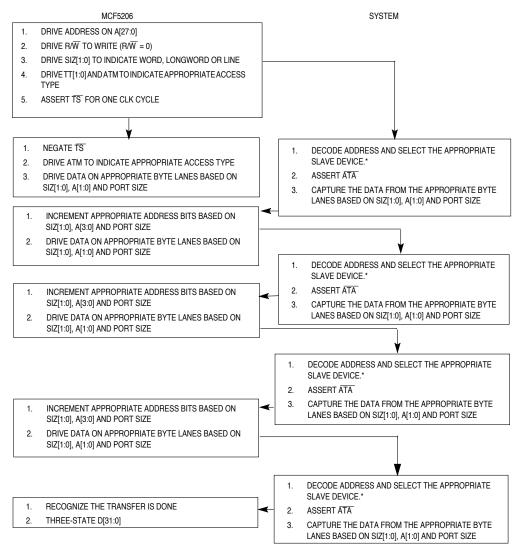

Figure 6-6 is a flowchart for write transfers to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer and the specific number of cycles needed for each transfer.

<sup>\*</sup>TO INSERT WAIT STATES, TA IS DRIVEN NEGATED.

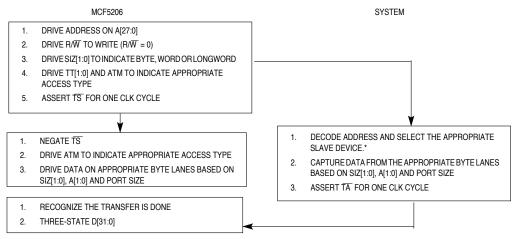

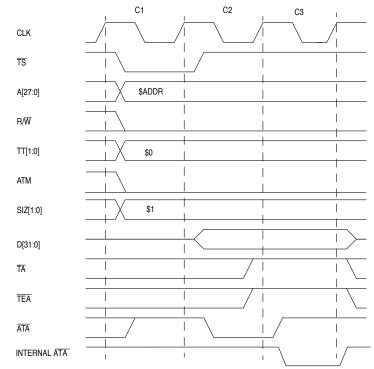

Figure 6-7 shows a supervisor data word-write transfer to a 16-bit port.

Figure 6-7. Word-Write Transfer to a 16-Bit Port (No Wait States)

## Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type. Access type and mode (ATM) identifies the transfer as writing data. The read/write (R/W) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$2 to indicate a word transfer. The MCF5206 asserts transfer start ( $\overline{TS}$ ) to indicate the beginning of a bus cycle.

## Clock 2 (C2)

During C2, the MCF5206 negates transfer start ( $\overline{TS}$ ), drives ATM high to identify the transfer as supervisor, and places the data on the data bus (D[31:0]). The selected device(s) asserts the transfer acknowledge ( $\overline{TA}$ ) if it is ready to latch the data. At the end of C2, the selected device latches the current value of D[31:16], and the MCF5206 samples the level of  $\overline{TA}$ . If  $\overline{TA}$  is asserted, the transfer of the word is complete and the transfer terminates. If  $\overline{TA}$  is negated, the MCF5206 continues to output the data and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted.

MCF5206 USER'S MANUAL Rev 1.0

## 6.5.2 Bursting Read Transfers: Word, Longword, and Line

If the burst-enable bit in the appropriate control register (Chip-Select Control Register or Default Memory Control Register) is set to 1 or the transfer is to DRAM, and the operand size is larger than the port size of the memory being accessed, the MCF5206 performs word, longword, and line transfers in burst mode. When burst mode is selected, the size of the transfer (indicated by SIZ[1:0]) will reflect the size of the operand being read, not the size of the port being accessed (i.e., a line transfer will be indicated by SIZ[1:0] = 3 and a longword transfer will be indicated by SIZ[1:0] = 0, regardless of the size of the port or the number of transfers required to access the entire set of data).

The MCF5206 supports burst-inhibited transfers for memory devices that cannot support bursting. For this type of bus cycle, you should clear the burst-enable bit in the Chip-Select Control Registers (CSCRs) or Default Memory Control Register (DMCR).

## NOTE

No burst-enable bit is provided for DRAM accesses. DRAM transfers are always bursted if the operand size is larger than the port size.

The MCF5206 uses line read transfers to access a 16-byte operand to support cache line filling and for a MOVEM instruction, when appropriate. A line read accesses a block of four longwords, aligned to a longword memory boundary, by supplying a starting address that points to one of the longwords and incrementing A3, A2, A1, and A0 of the supplied address for each transfer. A longword read accesses a single longword aligned to a longword boundary and increments A1 and A0 if the accessed port size is smaller than 32 bits. A word read accesses a single word of data, aligned to a word boundary and increments A0 if the accessed port size is smaller than 16 bits.

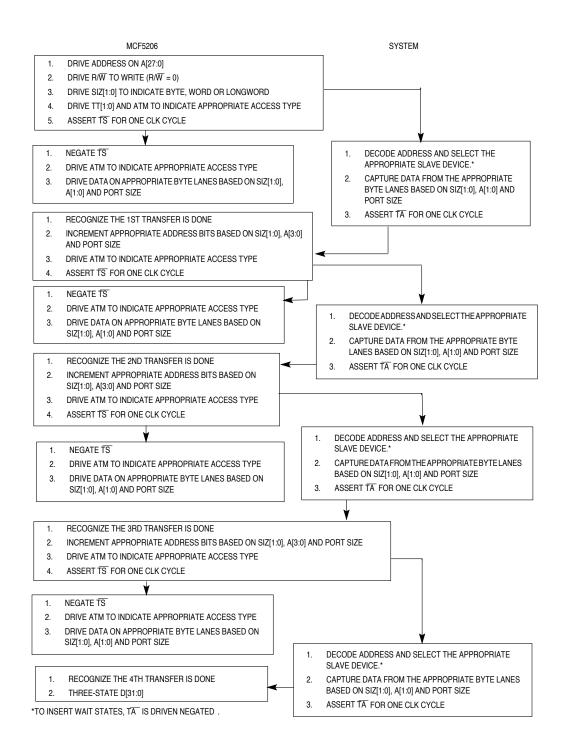

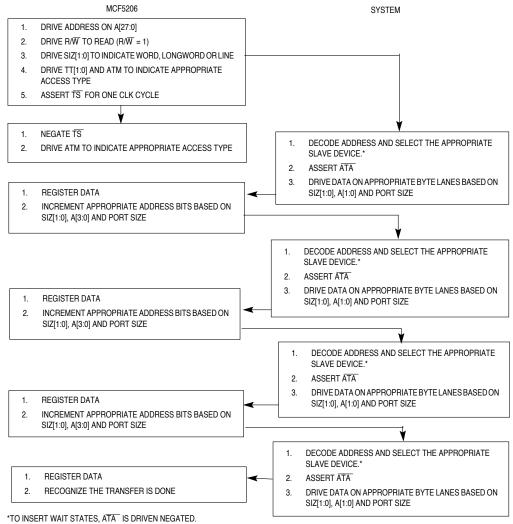

Figure 6-8 is a flowchart for bursting read transfers to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each

# transfer. A bursted read transfer can be from two to sixteen transfers long. The flowchart shown in Figure 6-8 is for a bursting transfer of four transfers long.

\*TO INSERT WAIT STATES, TA IS DRIVEN NEGATED.

## Figure 6-8. Bursting Word-, Longword-, and Line-Read Transfer Flowchart

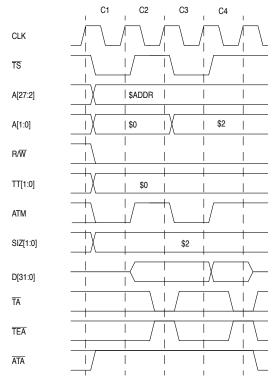

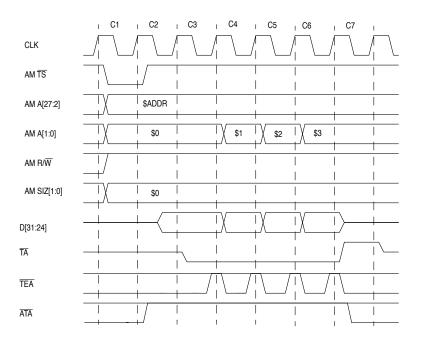

Figure 6-9 shows a bursting user code word-read transfer from an 8-bit port.

Figure 6-9. Bursting Word-Read From an 8-Bit Port (No Wait States)

Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type. Access transfer and mode (ATM) identifies the transfer as reading code. The read/write (R/W) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$2 to indicate a word transfer. The MCF5206 asserts transfer start (TS) to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM low to identify the transfer as user. The selected device(s) places the first byte of the addressed data on to D[31:24] and asserts the transfer acknowledge (TA). At the end of C2, the MCF5206 samples the level of TA and if TA is asserted, latches the current value of D[31:24]. If TA is asserted, the transfer of the first byte of the word read is complete. If TA is negated, the MCF5206 continues to sample TA and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample TA on successive rising edges of CLK until it is asserted.

MOTOROLA

Clock 3 (C3)

The MCF5206 increments A0 to address the next byte of the word transfer. The selected device(s) places the second byte of the addressed data onto D[31:24] and asserts the transfer acknowledge (TA). At the end of C3, the MCF5206 samples the level of TA and if TA is asserted, latches the current value of D[31:24]. If TA is asserted, the transfer of the word read is complete and the transfer is terminated. If TA is negated, the MCF5206 continues to sample TA and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample TA on successive rising edges of CLK until it is asserted.

## 6.5.3 Bursting Write Transfers: Word, Longword, and Line

The MCF5206 uses line-write transfers to access a 16-byte operand for a MOVEM instruction, when appropriate. A line write accesses a block of four longwords, aligned to a longword memory boundary, by supplying a starting address that points to one of the longwords and increments A3, A2, A1, and A0 of the supplied address for each transfer. A longword write accesses a single longword aligned to a longword boundary and increments A1 and A0 if the accessed port size is smaller than 32 bits. A word write accesses a single word of data, aligned to a word boundary and increments A0 if the accessed port size is smaller than 16 bits. Table 6-9 lists the encodings for the SIZx bits for each port size for transfers where bursting is both enabled and disabled.

|                 | 32-BIT PORT |               |      |                | 16 -BIT | PORT          |      | 8-BIT PORT     |      |               |      |                |

|-----------------|-------------|---------------|------|----------------|---------|---------------|------|----------------|------|---------------|------|----------------|

| OPERAND<br>SIZE |             | sting<br>Bled |      | STING<br>BITED |         | sting<br>Bled |      | sting<br>Bited |      | sting<br>Bled |      | STING<br>BITED |

|                 | SIZ1        | SIZ0          | SIZ1 | SIZ0           | SIZ1    | SIZ0          | SIZ1 | SIZ0           | SIZ1 | SIZ0          | SIZ1 | SIZ0           |

| BYTE            | 0           | 1             | 0    | 1              | 0       | 1             | 0    | 1              | 0    | 1             | 0    | 1              |

| WORD            | 1           | 0             | 1    | 0              | 1       | 0             | 1    | 0              | 1    | 0             | 0    | 1              |

| LONGWORD        | 0           | 0             | 0    | 0              | 0       | 0             | 1    | 0              | 0    | 0             | 0    | 1              |

| LINE            | 1           | 1             | 0    | 0              | 1       | 1             | 1    | 0              | 1    | 1             | 0    | 1              |

Table 6-9. SIZx Encoding for Burst- and Bursting-Inhibited Ports

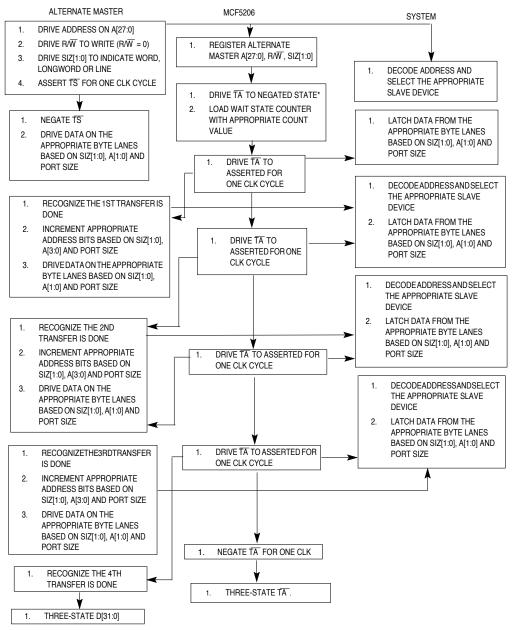

Figure 6-10 is a flowchart for bursting write transfers to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer and the specific number of cycles needed for each transfer. A bursted write transfer can be from two to sixteen transfers long. The flowchart in Figure 6-10 is for a bursting transfer of four transfers long.

\*TO INSERT WAIT STATES, TA IS DRIVEN NEGATED .

## Figure 6-10. Word-, Longword-, and Line-Write Transfer Flowchart

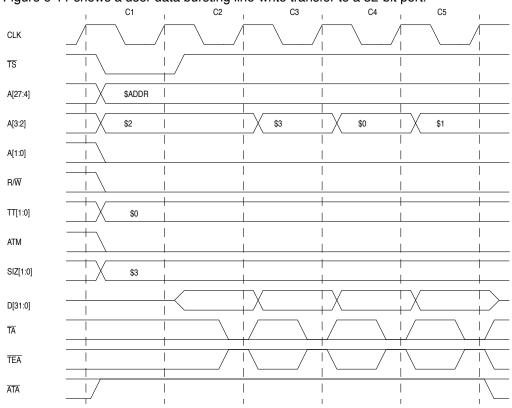

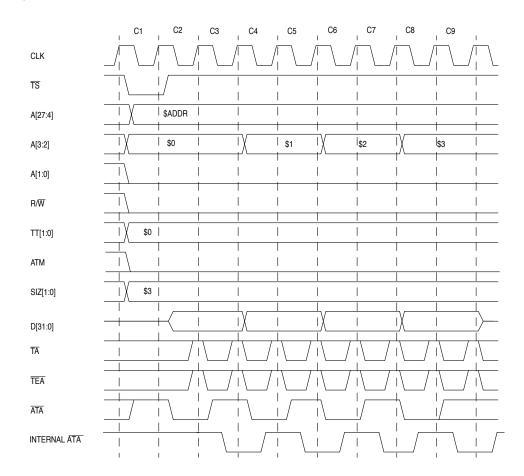

Figure 6-11 shows a user data bursting line-write transfer to a 32-bit port.

Figure 6-11. Line-Write Transfer to a 32-Bit Port (No Wait States)

Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type. Access type and mode (ATM) identifies the transfer as data. The read/write (R/W) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$3 to indicate a line transfer. The MCF5206 asserts transfer start ( $\overline{TS}$ ) to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM low to identify the transfer as user, and places the data on the data bus (D[31:0]). The selected device(s) asserts the transfer acknowledge ( $\overline{TA}$ ) if it is ready to latch the data. At the end of C2, the selected device latches the current value of D[31:0], and the MCF5206 samples the level of  $\overline{TA}$ . If  $\overline{TA}$  is asserted, the transfer of the first longword is complete. If  $\overline{TA}$  is negated, the MCF5206

MCF5206 USER'S MANUAL Rev 1.0

continues to output the data and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted.

Clock 3 (C3)

The MCF5206 increments A[3:2] to address the next longword of the line transfer and drives D[31:0] with the second longword of data. The selected device(s) asserts the TA if it is ready to latch the data. At the end of C3, the MCF5206 samples the level of TA and if TA is asserted, the second longword transfer of the line write is complete. If TA is negated, the MCF5206 continues to sample TA and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample TA on successive rising edges of CLK until it is asserted.

#### Clock 4 (C4)

This clock is identical to C3, except that once  $\overline{TA}$  is asserted, the value corresponds to the third longword of data for the burst.

## Clock 5 (C5)

This clock is identical to C3, except that once  $\overline{TA}$  is asserted, the data value corresponds to the fourth longword of data for the burst. This is the last CLK cycle of the line-write transfer and the MCF5206 three-states D[31:0] at the start of the next CLK cycle.

## 6.5.4 Burst-Inhibited Read Transfer: Word, Longword, and Line

If the burst-enable bit in the appropriate control register (Chip-Select Control Register or Default Memory Control Register) is cleared and the operand size is larger than the port size of the memory being accessed, the MCF5206 performs word, longword, and line transfers in burst-inhibited mode. When burst-inhibit mode is selected, the size of the transfer (indicated by SIZ[1:0]) will reflect the port size if the operand being read is larger than the port size or the operand size if the port size is larger than the operand size. A transfer size of line (SIZ[1:0] = 3) will never be indicated in burst-inhibited mode. If the operand size is line, the size pins (SIZ[1:0]) will always indicate the port size. Refer to Table 6-9 for SIZx encodings for each port size for burst-inhibited transfers.

## NOTE

All transfers to DRAM that have an operand size larger than the port size are bursted. Burst-inhibited transfers cannot be generated for DRAM accesses.

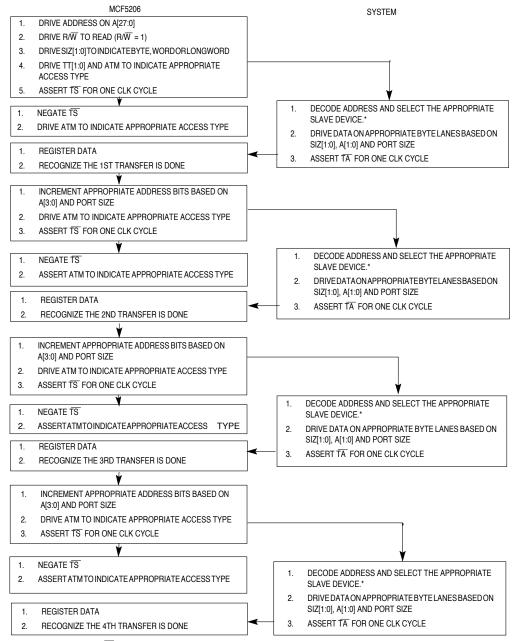

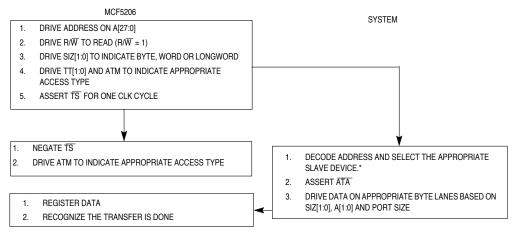

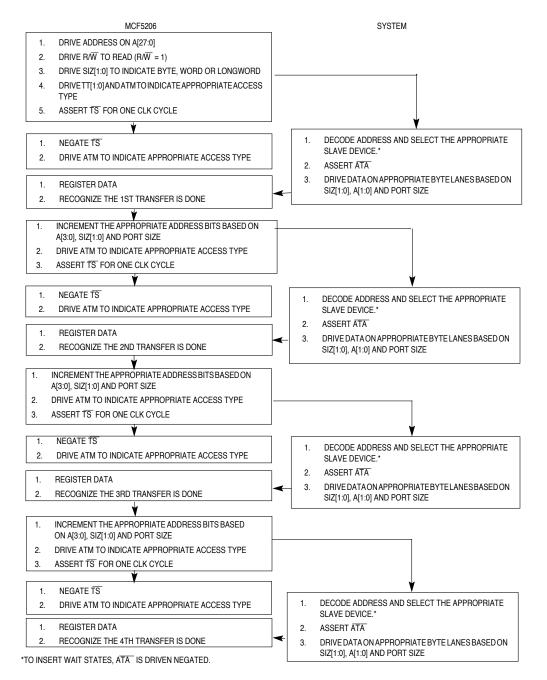

The basic transfer of a burst-inhibited read is the same as a "normal" read with the addition of more transfers until the entire operand has been accessed. Burst-inhibited read transfers can be from two to sixteen transfers long. Figure 6-12 is a flowchart for burst-inhibited read transfers (4 transfers long) to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer.

MOTOROLA

\*TO INSERT WAIT STATES, TA IS DRIVEN NEGATED.

MCF5206 USER'S MANUAL Rev 1.0

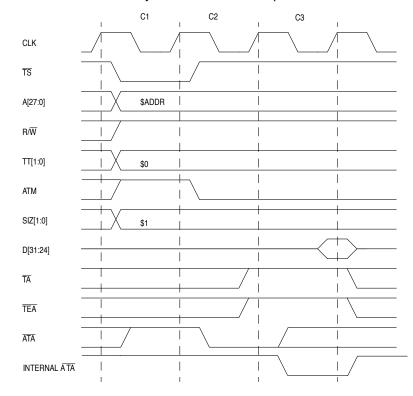

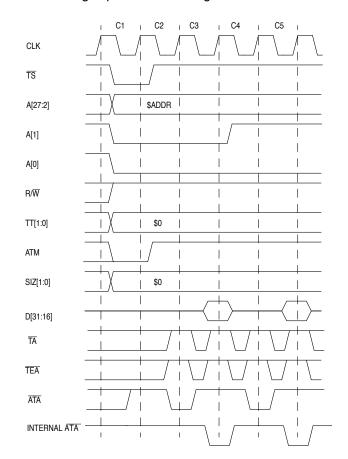

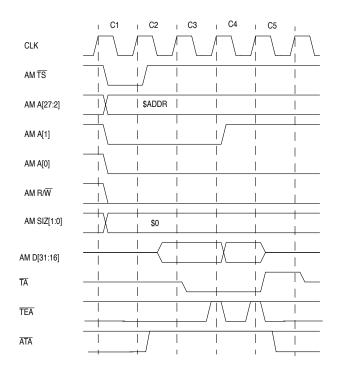

Figure 6-13 shows a burst-inhibited supervisor code longword-read transfer from an 8-bit port.

#### Figure 3-13. Burst-Inhibited Longword Read From an 8-Bit Port (No Wait States)

Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and drives ATM high to identify the transfer as code. The read/write (R/W) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$1 to indicate a byte transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$  and drives ATM high to identify the transfer as supervisor. The selected device(s) places the first byte of the addressed data onto D[31:24] and asserts  $\overline{TA}$ . At the end of C2, the MCF5206 samples the level of  $\overline{TA}$  and if TA is asserted, latches the current value of D[31:24]. If TA is asserted, the transfer of the first byte of the longword read is complete. If TA is negated, the MCF5206 continues to

MOTOROLA

sample  $\overline{TA}$  and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted.

Clock 3 (C3)

The MCF5206 increments A[1:0] to address the second byte of the longword transfer. The MCF5206 continues to drive transfer type (TT[1:0]), read/write (R/W) and size (SIZ[1:0]) signals to indicate a byte read. Access transfer mode (ATM) is driven high to indicate the transfer as code. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of the second transfer of the bus cycle.

Clock 4 (C4)

This clock is identical to C2, except that once  $\overline{TA}$  is recognized asserted, the latched value corresponds to the second byte of data for the longword transfer.

Clock 5 (C5)

This clock is identical to C3, except the address is incremented to address the third byte of the longword transfer.

Clock 6 (C6)

This clock is identical to C2, except that once  $\overline{TA}$  is recognized asserted, the latched value corresponds to the third byte of data for the longword transfer.

Clock 7 (C7)

This clock is identical to C3, except the address is incremented to address the fourth byte of the longword transfer.

Clock 8 (C8)

This clock is identical to C2, except that once  $\overline{TA}$  is recognized asserted, the latched value corresponds to the fourth byte of data for the longword. This is the last CLK cycle of the longword-read transfer. The selected device negates  $\overline{TA}$  signal and three-states D[31:24] after the next rising edge of CLK.

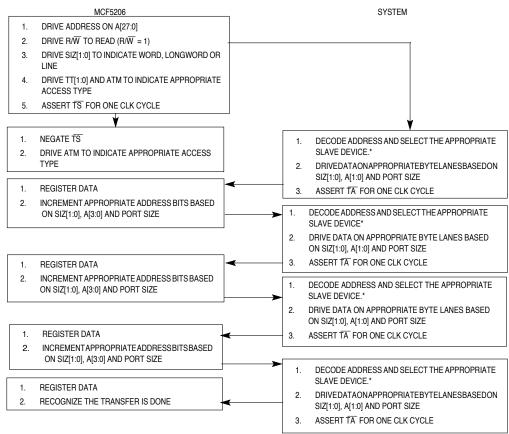

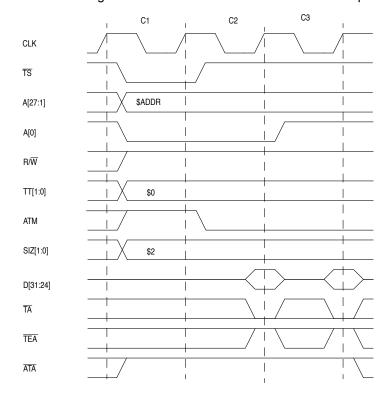

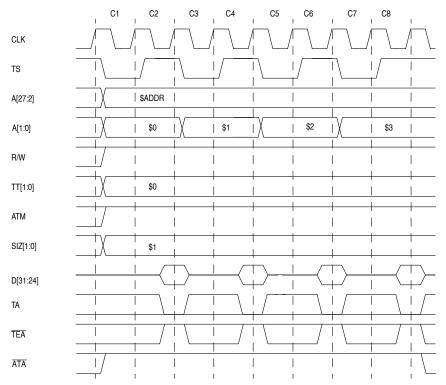

## 6.5.5 Burst-Inhibited Write Transfer: Word, Longword, and Line

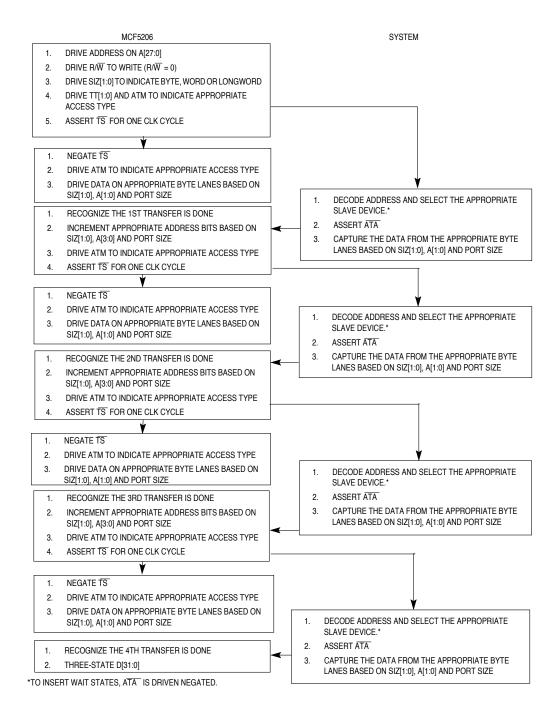

The basic transfer of a burst-inhibited write is the same as "normal" write with the addition of more transfers until the entire operand has been accessed. Burst-inhibited write transfers can be from 2 to 16 transfers long. Figure 6-14 is a flowchart for burst-inhibited write transfers (4 transfers long) to 8-, 16-, or 32-bit ports. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer.

MCF5206 USER'S MANUAL Rev 1.0

MCF5206 USER'S MANUAL Rev 1.0

6-25

#### Figure 6-14. Burst-Inhibited Byte-, Word-, and Longword-Write Transfer Flowchart

Figure 6-15 shows a burst-inhibited supervisor data longword-write transfer to a 16-bit port.

# Figure 6-15. Burst-Inhibited Longword-Write Transfer to a 16-Bit Port (No Wait States)

Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as data. The read/write ( $R/\overline{W}$ ) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$2 to indicate a word transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

## Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM high to identify the transfer as supervisor and places the data on the data bus (D[31:0]). The selected device(s) asserts  $\overline{TA}$  if it is ready to latch the data. At the end of C2, the selected device latches the current

MCF5206 USER'S MANUAL Rev 1.0

MOTOROLA

6-26

value of D[31:16], and the MCF5206 samples the level of  $\overline{TA}$ . If  $\overline{TA}$  is asserted, the transfer of the first word is complete. If  $\overline{TA}$  is negated, the MCF5206 continues to output the data and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted.

Clock 3 (C3)

The MCF5206 increments A[1:0] to address the next word, asserts  $\overline{TS}$  and drives ATM low to identify the transfer as code or data.

Clock 4 (C4)

This clock is identical to C2, except that the data driven corresponds to the second word of data. This is the last CLK cycle of the longword-write transfer and the MCF5206 three-states D[31:0] at the start of the next CLK cycle.

## 6.5.6 Asynchronous-Acknowledge Read Transfer

The MCF5206 provides an asynchronous acknowledge that can be used for termination of all MCF5206 transfers except accesses to DRAM. ATA is synchronized internally before being used and must meet the specified setup and hold times to CLK only if recognition by a specific CLK rising edge is required. Because of the internal synchronization of ATA, data must be driven on the bus until the asynchronous transfer acknowledge is recognized internally. If transfer error acknowledge (TEA) is asserted while ATA is being synchronized internally, the transfer will be terminated in an error.

## NOTE

The internal synchronized version of  $(\overline{ATA})$  will be referred to as "internal asynchronous transfer acknowledge." Because of the time required to internally synchronize  $\overline{ATA}$  during a read cycle, data is latched on the rising edge of CLK when the internal asynchronous transfer acknowledge is asserted. Consequently, data must remain valid for at least one CLK cycle after the assertion of  $\overline{ATA}$ . Similarly, during a write cycle, data is driven until the rising edge of CLK when the internal asynchronous transfer acknowledge is asserted.

Figure 6-16 is a flowchart for read transfers to 8-, 16-, or 32-bit ports with asynchronous termination. Bus operations are similar for each case and vary only with the size indicated,

the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer.

\*TO INSERT WAIT STATES, ATA IS DRIVEN NEGATED.

## Figure 6-16. Byte-, Word-, and Longword-Read Transfer with Asynchronous Termination Flowchart (One Wait State)

## NOTE

Zero-wait-state operation can be achieved with asynchronous termination by asserting asynchronous termination acknowledge (ATA) during the CLK cycle transfer start (TS) is asserted. This may only be practical if  $\overline{\text{ATA}}$  is tied to GND. Refer to **3.5.12 Termination Tied to GND** for more information.

Figure 6-17 shows a user code byte read from an 8-bit port.

Figure 6-17. Byte-Read Transfer from an 8-Bit Port Using Asynchronous Termination (One Wait State)

Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as code. The read/write (R/W) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$1 to indicate a byte transfer. The MCF5206 asserts TS to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$  and drives ATM low to identify the transfer as user. The selected device(s) asserts  $\overline{ATA}$ .

Clock 3 (C3)

At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, latches the current value of D[31:24]. If internal

MOTOROLA

asynchronous transfer acknowledge is asserted, the byte transfer is complete and the transfer terminates. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge until it is asserted. As long as ATA is asserted by the falling edge of C2, internal asynchronous transfer acknowledge the will be asserted by the rising edge of C3.

## 6.5.7 Asynchronous Acknowledge Write Transfer

Figure 6-18 is a flowchart for write transfers to 8-, 16-, or 32-bit ports with asynchronous termination. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer.

\*TO INSERT WAIT STATES, ATA IS DRIVEN NEGATED.

## Figure 6-18. Byte-, Word-, and Longword-Write Transfer with Asynchronous Termination Flowchart

Figure 6-19 shows a user data byte transfer to a 32-bit port with asynchronous termination.

# Figure 6-19. Byte-Write Transfer to a 32-Bit Port Using Asynchronous Termination (One Wait State)

Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as data. The read/write (R/W) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$1 to indicate a byte transfer. The MCF5206 asserts TS to indicate the beginning of a bus cycle.

#### Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM low to identify the transfer as user and places the data on the data bus (D[31:0]). The selected slave device asserts  $\overline{ATA}$ . The selected slave device may latch the data present on the data bus or may wait until the end of Clock 3 (after internal asynchronous transfer acknowledge has been asserted).

MOTOROLA

Clock 3 (C3)

At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, the transfer of the byte is complete and the transfer terminates. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge until it is asserted. As long as ATA is asserted by the falling edge of C2, internal asynchronous transfer acknowledge will be asserted by the rising edge of C3.

# 6.5.8 Bursting Read Transfers: Word, Longword, and Line with Asynchronous Acknowledge

If the burst-enable bit in the appropriate Chip-Select Control Register (CSCR) or Default Memory Control Register (DMCR) is set to 1 and the operand size is larger than the port size of the memory being accessed, the MCF5206 performs word, longword, and line transfers in burst mode. When burst mode is selected and the transfer is not to DRAM, the transfer can be terminated synchronously using TA, or asynchronously using ATA. The transfer attributes are the same for both the synchronous and asynchronously terminated burst transfers.

Figure 6-20 is a flowchart for bursting read transfers to 8-, 16-, or 32-bit ports using asynchronous termination. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus needed for the transfer, and the specific number

of cycles used for each transfer. A bursted transfer can be from two to 16 transfers long. The flow chart shown is for four bursting transfers.

#### Figure 6-20. Bursting Word-, Longword-, and Line-Read Transfer with Asynchronous Termination Flowchart

Figure 6-21 shows a bursting supervisor data longword-read transfer from a 16-bit port.

Figure 6-21. Bursting Longword-Read from 16-Bit Port Using Asynchronous Termination (One Wait State)

Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as reading data. The read/write (R/W) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$0 to indicate a longword transfer. The MCF5206 asserts TS to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM high to identify the transfer as supervisor. The selected device(s) asserts  $\overline{ATA}$ .

Clock 3 (C3)

At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, latches the current value of D[31:16]. If internal asynchronous transfer acknowledge is asserted, the transfer of the first word is complete. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge as a TTA is asserted by the falling edge of C2, internal asynchronous transfer acknowledge will be asserted by the rising edge of C3.

Clock 4 (C4)

The MCF5206 increments A[1:0] to address the next word. The selected device(s) asserts ATA.

Clock 5 (C5)

At the end of C5, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, latches the current value of D[31:16]. If internal asynchronous transfer acknowledge is asserted, the transfer of the second word is complete and the transfer is terminated. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge until it is asserted. As long as ATA is asserted by the falling edge of C4, internal asynchronous transfer acknowledge will be asserted by the rising edge of C5.

# 6.5.9 Bursting Write Transfers: Word, Longword, and Line with Asynchronous Acknowledge

Figure 6-22 is a flowchart for bursting write transfers (four transfers long) to 8-, 16-, or 32bit ports using asynchronous termination. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer. A bursted transfer can be from two to 16 transfers long.

\*TO INSERT WAIT STATES, ATA IS DRIVEN NEGATED.

# Figure 6-22. Word-, Longword-, and Line-Write Transfer Flowchart with Asynchronous Termination

Figure 6-23 shows a bursting user data line-write transfer to a 32-bit port using asynchronous termination.

Figure 6-23. Bursting Line-Write from 32-Bit Port Using Asynchronous Termination (One Wait State)

Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as data. The read/write ( $R/\overline{W}$ ) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$3 to indicate a line transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

MOTOROLA

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM low to identify the transfer as user and places the data on the data bus (D[31:0]). The selected device(s) asserts  $\overline{ATA}$  if it is ready to latch the data.

Clock 3 (C3)

If the selected device asserted asynchronous transfer acknowledge during C2, the selected device must latch the data by the end of C3. At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge. If internal asynchronous transfer acknowledge is negated, the first longword is complete. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge until it is asserted. As long as ATA is asserted by the falling edge of C2, the internal asynchronous transfer acknowledgewill be asserted by the rising edge of C3.

Clock 4 (C4)

The MCF5206 increments A[3:2] to address the next longword of the line transfer and drives D[31:0] with the second longword of data. The selected device(s) asserts  $\overline{ATA}$  if it is ready to latch the data. At the end of C4, the MCF5206 samples the level of internal  $\overline{ATA}$  and if it is asserted, the second longword transfer of the line write is complete. If internal  $\overline{ATA}$  is negated, the MCF5206 continues to sample internal  $\overline{ATA}$  and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal  $\overline{ATA}$  on successive rising edge of CLK until it is asserted.

Clock 5 (C5)

This clock is identical to C3, except that the data value corresponds to the second longword of data for the burst.

Clock 6 (C6)

This clock is identical to C4, except that once internal ATA is asserted, the address and the data values correspond to the third longword of data for the burst.

Clock 7 (C7)

This clock is identical to C3, except that the data value corresponds to the third longword of data for the burst.

Clock 8 (C8)

This clock is identical to C4, except that once internal ATA is asserted the address and data value correspond to the fourth longword of data for the burst.

MCF5206 USER'S MANUAL Rev 1.0

MOTOROLA

6-38

Clock 9 (C9)

This clock is identical to C3, except that the data value corresponds to the fourth longword of data for the line. This is the last CLK cycle of the line write transfer and the MCF5206 three-states D[31:0] at the start of the next CLK cycle.

# 6.5.10 Burst-Inhibited Read Transfers: Word, Longword, and Line with Asynchronous Acknowledge

If the burst-enable bit is cleared in the appropriate Chip-Select Control Register (CSCR) or Default Memory Control Register (DMCR) and the operand size is larger than the port size of the memory being accessed, the MCF5206 performs word, longword, and line transfers in burst-inhibited mode. When burst-inhibit mode is selected, the size of the transfer (indicated by SIZ[1:0]) will reflect the port size if the operand being read is larger than the port size of line (SIZ[1:0] = 33) will never be indicated in burst-inhibited mode. If the operand size is line, the size pins (SIZ[1:0]) will always indicate the port size.

The basic transfer of a burst-inhibited read using asynchronous termination is the same as "normal" read using asynchronous termination with the addition of more transfers, until the entire operand has been accessed. Figure 6-24 is a flowchart for burst-inhibited read transfers to 8-, 16-, or 32-bit ports with asynchronous termination. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer. The flowchart is specifically for a burst-inhibited transfer of four transfers long.

Figure 6-24. Burst-Inhibited Word-, Longword-, and Line-Read Transfer with Asynchronous Termination Flowchart

MCF5206 USER'S MANUAL Rev 1.0

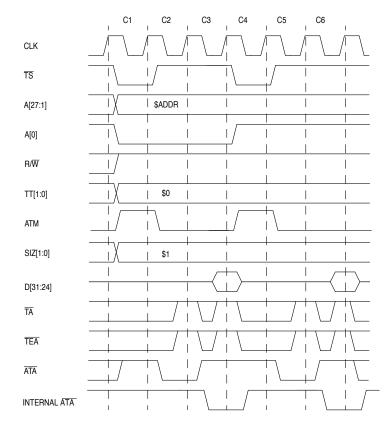

Figure 6-25 shows a burst-inhibited user code word-read transfer from an 8-bit port.

Figure 6-25. Burst-Inhibited Word Read from 8-Bit Port Using Asynchronous Termination

Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as code. The read/write (R/W) signal is driven high for a read cycle and the size signals (SIZ[1:0]) are driven to \$1 to indicate a byte transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM low to identify the transfer as user. The selected device(s) asserts  $\overline{ATA}$ .

Clock 3 (C3)

At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, latches the current value of D[31:24]. If internal asynchronous transfer acknowledge is asserted, the transfer of the first byte is complete. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge will be asserted by the falling edge of C2, internal asynchronous transfer acknowledge will be asserted by the rising edge of C3.

Clock 4 (C4)

This clock is identical to C1, except the address bus is incremented to point to the second byte of data.

Clock 5 (C5)

This clock is identical to C2.

Clock 6 (C6)

This clock is identical to C3, except once internal ATA is recognized, the data corresponds to the second byte of data.

# 6.5.11 Burst-Inhibited Write Transfers: Word, Longword, and Line with Asynchronous Acknowledge

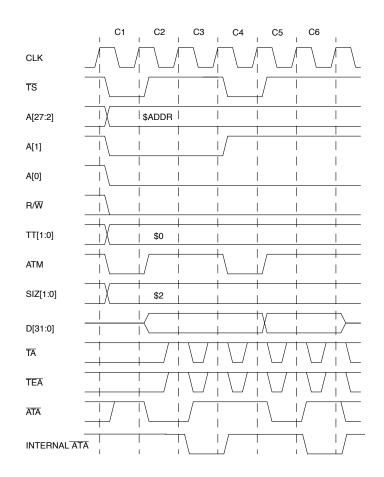

The basic transfer of a burst-inhibited write using asynchronous termination is the same as "normal" write transfers with asynchronous termination but with the addition of more transfers until the entire operand has been accessed. Figure 6-26 is a flowchart for burst-inhibited write transfers to 8-, 16-, or 32-bit ports using asynchronous termination. Bus operations are similar for each case and vary only with the size indicated, the portion of the data bus used for the transfer, and the specific number of cycles needed for each transfer. The flowchart specifically depicts a burst-inhibited transfer of four accesses long.

MCF5206 USER'S MANUAL Rev 1.0

MOTOROLA

#### **Asynchronous Termination Flowchart**

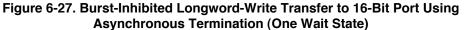

Figure 6-27 shows a burst-inhibited supervisor data longword-write transfer to a 16-bit port.

Clock 1 (C1)

The write cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as data. The read/write ( $R/\overline{W}$ ) signal is driven low for a write cycle, and the size signals (SIZ[1:0]) are driven to \$2 to indicate a word transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

MCF5206 USER'S MANUAL Rev 1.0

MOTOROLA

6-44

Clock 2 (C2)

During C2, the MCF5206 negates  $\overline{TS}$ , drives ATM high to identify the transfer as supervisor and drives the data on the data bus (D[31:0]). The selected device(s) asserts  $\overline{ATA}$  if it is ready to latch the data.

Clock 3 (C3)

At the end of C3, the MCF5206 samples the level of internal asynchronous transfer acknowledge and if it is asserted, terminates the first word transfer. If internal asynchronous transfer acknowledge is asserted, the transfer of the first word is complete. If internal asynchronous transfer acknowledge is negated, the MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample internal asynchronous transfer acknowledge of C3, the rising edge of C3 will assert the internal asynchronous transfer acknowledge.

Clock 4 (C4)

This clock is identical to C1, except the MCF5206 increments the address to indicate the next word.

Clock 5 (C5)

This clock is identical to C2, except that the data driven corresponds to the second word of data.

Clock 6 (C6)

This clock is identical to C3, except after asynchronous transfer acknowledge is recognized, the MCF5206 three-states the data bus after the next rising edge of CLK.

## 6.5.12 Termination Tied to GND

If the MCF5206 is in a system with multiple masters and you require zero wait-state operation, you can tie  $\overline{ATA}$  to GND to achieve zero wait-state operation for nonDRAM transfers.  $\overline{ATA}$  must be used in this case as the MCF5206 can drive  $\overline{TA}$  during alternate master accesses. When  $\overline{ATA}$  is tied to GND, all nonDRAM transfers follow the timing shown with  $\overline{TA}$  asserted with zero wait states.

If the MCF5206 is the only master in the system,  $\overline{TA}$  and  $\overline{BG}$  can be tied to GND to grant mastership of the external bus to the MCF5206 and achieve zero wait-state operation.

MOTOROLA

#### NOTE

$\overline{TA}$  cannot be tied to GND if the MCF5206 is not the only bus master in the system. Damage to the part could occur if  $\overline{TA}$  is tied to GND and alternate master accesses using 5206 generated termination.

### 6.6 MISALIGNED OPERANDS

All MCF5206 data formats can be located in memory on any byte boundary. A byte operand is properly aligned at any address; a word operand is misaligned at an odd address; and a longword is misaligned at an address that is not evenly divisible by four. However, because operands can reside at any byte boundary, they can be misaligned. Although the MCF5206 does not enforce any alignment restrictions for data operands (including program counter (PC) relative data addressing), some performance degradation occurs when additional bus cycles are required for longword or word operands that are misaligned. For maximum performance, data items should be aligned on their natural boundaries. All instruction words and extension words must reside on word boundaries. An address error exception will occur with any attempt to prefetch an instruction word at an odd address.

The MCF5206 converts misaligned operand accesses that are noncacheable to a sequence of aligned accesses. Figure 6-28 illustrates the transfer of a longword operand from a byte address to a 32-bit port, requiring more than one bus cycle. In this example, the SIZ[1:0] signals specify a byte transfer, and the byte offset of \$1. The slave device supplies the byte and acknowledges the data transfer. When the MCF5206 starts the second cycle, the SIZ[1:0] signals specify a word transfer with a byte offset of \$2. The next two bytes are transferred during this cycle. The MCF5206 then initiates the third cycle, with the SIZ[1:0] signals indicating a byte transfer. The byte offset is now \$0; the port supplies the final byte and the operation is complete. Figure 6-29 is similar to the example illustrated in Figure 6-28 except that the operand is word-sized and the transfer requires only two bus cycles.

|            | 31 24 | 23 16 | 15 8 | 7 0  |

|------------|-------|-------|------|------|

| TRANSFER 1 | -     | OP 3  | -    | -    |

| TRANSFER 2 | -     | -     | OP 2 | OP 1 |

| TRANSFER 3 | OP 0  | -     | -    | -    |

#### Figure 6-28. Example of a Misaligned Longword Transfer

|            | 31 24 | 23 16 | 15 8 | 7 0  |

|------------|-------|-------|------|------|

| TRANSFER 1 | -     | -     | -    | OP 1 |

| TRANSFER 2 | OP 0  | -     | -    | -    |

#### Figure 6-29. Example of a Misaligned Word Transfer

#### NOTE

Alternate masters that are using internal MCF5206 chipselect, DRAM, and default memory control signals must initiate aligned transfers only.

## 6.7 ACKNOWLEDGE CYCLES

When a peripheral device requires the services of the MCF5206 or is ready to send information that the ColdFire core requires, it can signal the ColdFire core to take an interrupt exception. The interrupt exception transfers control to a routine that responds appropriately. The peripheral device uses the interrupt priority-level/interrupt-request signals (IPLx/IRQx) to signal an interrupt condition to the MCF5206.

The MCF5206 has two levels of interrupt masking. The first level of interrupt masking is in the interrupt controller in the System Integration Module (SIM) which masks individual interrupt inputs and then outputs the interrupt priority level of the highest pending unmasked interrupt to the ColdFire core. The Status Register (SR) provides the second level of interrupt masking in the ColdFire core which contains an interrupt priority mask. The value of the SR interrupt mask is the highest priority level that the ColdFire core ignores. When an interrupt request has a priority higher than the value in the mask, the ColdFire core makes the request a pending interrupt. For more information about the Status Register refer to **Section 3.2.2.1 Status Register** in the ColdFire Core Section.

The MCF5206 continuously samples the external interrupt input signals and synchronizes and debounces these signals. An interrupt request must be held constant for at least two consecutive CLK periods to be considered a valid input. If the external interrupt inputs are programmed to individual interrupt requests (at levels 1, 4, and 7), the interrupt request must maintain the interrupt request level until the MCF5206 acknowledges the interrupt to guarantee that the interrupt is recognized. If the external interrupt request level or a higher priority level, the interrupt request must maintain the interrupt request level or a higher priority level until the MCF5206 acknowledges the interrupt to guarantee that the interrupt request must maintain the interrupt request level or a higher priority level until the MCF5206 acknowledges the interrupt to guarantee that the interrupt are programmed to move the move and the mCF5206 acknowledges the interrupt request level or a higher priority level until the MCF5206 acknowledges the interrupt to guarantee that the interrupt is recognized.

## NOTE

All interrupts are level sensitive only. Interrupts must remain stable and held valid for the interrupt to be detected.

The MCF5206 takes an interrupt exception for a pending interrupt within one instruction boundary after processing any other pending exception with a higher priority. Thus, the MCF5206 executes at least one instruction in an interrupt exception handler before recognizing another interrupt request.

If the AVEC bit in the Interrupt Control Register (ICR) for the interrupt being acknowledged is set to 1 (enabling autovectoring), the interrupt acknowledge vector will be generated internally and no interrupt acknowledge cycle will be generated on the external bus. Refer

MOTOROLA

to the SIM section **Section 7.3.2.3 Interrupt Control Register (ICR)** for ICR programming.

### NOTE

If autovector generation is used for external interrupts, no interrupt acknowledge cycle will be generated on the external bus. Consequently, you must clear the external interrupt in the interrupt service routine.

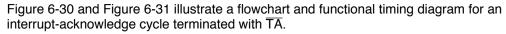

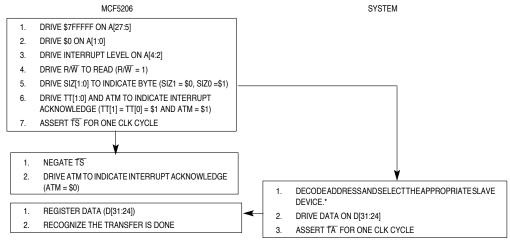

## 6.7.1 Interrupt Acknowledge Cycle

When the MCF5206 processes an interrupt exception, it performs an interrupt acknowledge bus cycle to obtain the vector number that contains the starting location of the interrupt exception handler.

The interrupt acknowledge bus cycle is a read transfer. It differs from a normal read cycle in the following respects:

- TT[1:0] = \$3 to indicate a CPU space/acknowledge bus cycle

- ATM = \$1 when  $\overline{TS}$  is asserted and ATM = \$0 when  $\overline{TS}$  is negated

- Address signals A[27:5] are set to all ones (\$7FFFF)

- · Address signals A[4:2] are set to the interrupt request level being acknowledged

- Address signals A[1:0] are set to all zeros (\$0)

The responding device places the vector number on D[31:24] of the data bus during the interrupt acknowledge bus cycle and the cycle is terminated normally with TA or  $\overline{ATA}$ .

Figure 6-30. Interrupt-Acknowledge Cycle Flowchart

Figure 6-31 shows an interrupt acknowledge cycle.

Figure 6-31. Interrupt Acknowledge Bus Cycle Timing (No Wait States)

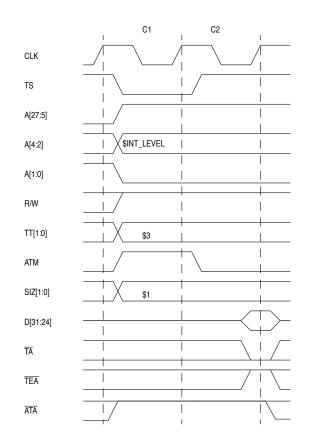

Clock 1 (C1)

The interrupt acknowledge cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The address bus is driven with \$7FFFFF on A[27:5], \$0 on A[1:0] and the interrupt level being acknowledged on A[4:2]. The transfer type (TT[1:0]) signals are driven to \$3 and the ATM is driven high to identify the access as an interrupt acknowledge cycle. The read/write (R/W) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$1 to indicate a byte transfer. The MCF5206 asserts  $\overline{TS}$  to indicate the beginning of a bus cycle.

### Clock 2 (C2)

During C2, the MCF5206 negates transfer start  $(\overline{TS})$ , drives access type and mode (ATM) low to identify the transfer as an interrupt acknowledge cycle. The selected device(s)

MCF5206 USER'S MANUAL Rev 1.0

places the interrupt vector number onto D[31:24] and asserts  $\overline{TA}$ . At the end of C2, the MCF5206 samples the level of  $\overline{TA}$  and if  $\overline{TA}$  is asserted, latches the current value of D[31:24] which contains the interrupt vector number. If  $\overline{TA}$  is asserted, the transfer of the interrupt vector is complete and the transfer terminates. If  $\overline{TA}$  is negated, the MCF5206 continues to sample  $\overline{TA}$  and inserts wait states instead of terminating the transfer. The MCF5206 continues to sample  $\overline{TA}$  on successive rising edges of CLK until it is asserted.

#### NOTE

Interrupt acknowledge cycles can be asynchronously acknowledged using ATA. As long as ATA is asserted by the falling edge of C2, internal asynchronous transfer acknowledge will be asserted by the rising edge of C3. The interrupt vector must remain driven on D[31:24] until internal asynchronous transfer acknowledge is asserted.

## 6.8 BUS ERRORS

The system hardware can use the transfer error acknowledge ( $\overline{TEA}$ ) signal to abort the current bus cycle when a fault is detected. A bus error is recognized during a bus cycle when  $\overline{TEA}$  is asserted.

When the MCF5206 recognizes a bus error condition for an access, the access is terminated immediately. An access that requires more than one transfer, aborts without completing the remaining transfers if  $\overline{\mathsf{TEA}}$  is asserted, regardless of whether the access uses burst or burst-inhibited transfers.

Figure 6-32 shows a bursting supervisor code longword-read access from a 16-bit port with a transfer error.

# Figure 6-32. Bursting Longword-Read Access from 16-Bit Port Terminated with TEA Timing

#### Clock 1 (C1)

The read cycle starts in C1. During C1, the MCF5206 places valid values on the address bus (A[27:0]) and transfer control signals. The transfer type (TT[1:0]) signals identify the specific access type and ATM identifies the transfer as code. The read/write ( $R/\overline{W}$ ) signal is driven high for a read cycle, and the size signals (SIZ[1:0]) are driven to \$0 to indicate a longword transfer. The MCF5206 asserts transfer start ( $\overline{TS}$ ) to indicate the beginning of a bus cycle.

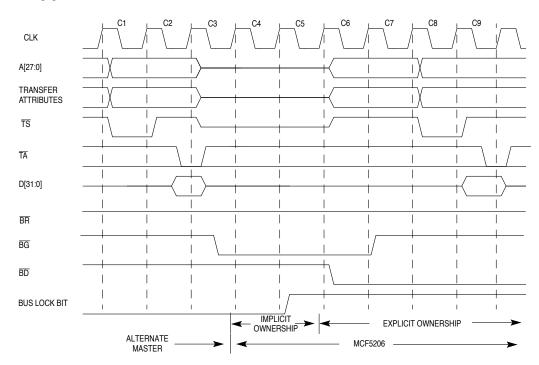

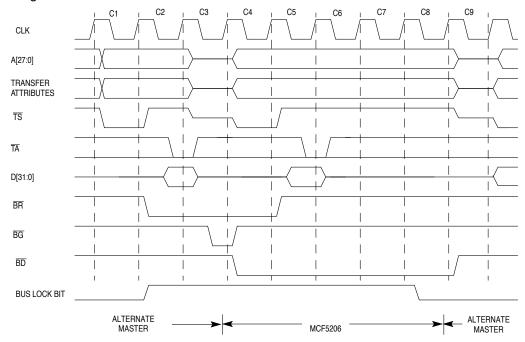

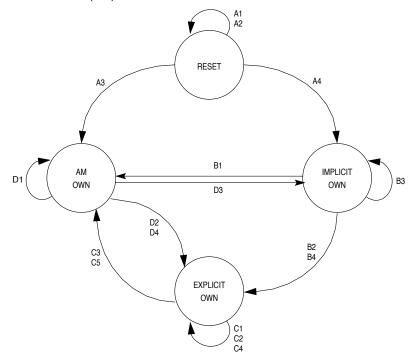

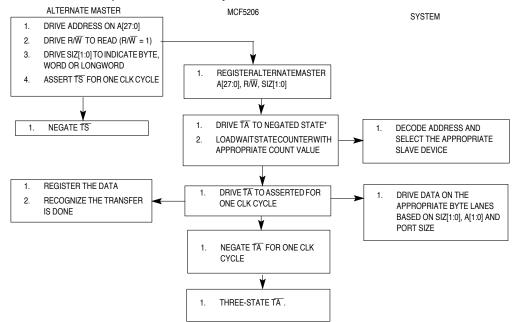

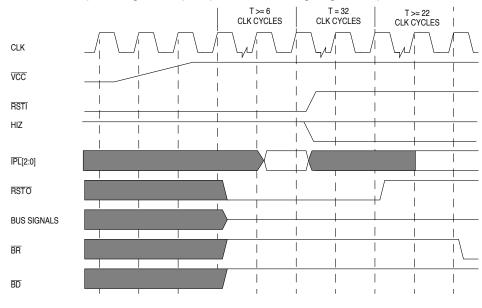

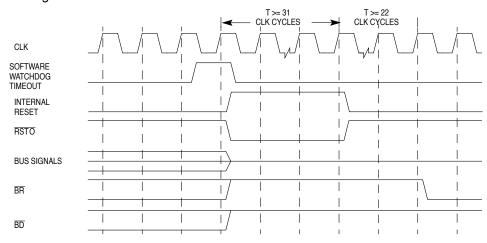

#### Clock 2 (C2)